# **IMPINJ MONZA R6-P**

## TAG CHIP DATASHEET IPJ-W1730-K00 IPJ-W1710-A00

Version 6.0

© 2020, Impinj, Inc.

www.impinj.com

## **OVERVIEW**

The Monza® R6-P RAIN RFID tag chip is optimized for serializing items such as apparel, electronics, cosmetics, pharmaceuticals, jewelry and various other products. It delivers unmatched read performance and data integrity for effective Item Intelligence applications and record-breaking encoding performance to enable the lowest applied tag cost.

With the addition of user memory and range-reduction switch, advanced usages such as loss prevention, brand protection and enhanced privacy are enabled. The Monza R6-P tag chip includes revolutionary technologies such as automatic performance adjustments and encoding diagnostics that reinforce the position of the Monza tag chip family as the RFID industry leader

## **FEATURES**

- Industry leading read sensitivity of up to -22.1 dBm with a dipole antenna, combined with excellent interference rejection, delivers exceptional read reliability

- Superior write sensitivity of up to -17.3 dBm with a dipole antenna for unparalleled encoding reliability

- Inlay compatibility between all Monza 6 family tag chips

- Fast memory write speed of 1.6 ms for 32 bits

- Encoding throughput up to 9,500 tags/minute using the Impinj ItemEncode™ software

- Up to 128 bits of EPC memory

- 96 bits of Serialized TID with 48-bit serial number

- Up to 64 bits of user memory

- RAIN RFID / ISO 18000-63 and EPCglobal Gen2v2 compliant

- Unmatched data integrity with Integra™ Technology for encoding diagnostics

- Maintains performance across different dielectrics with AutoTune™ Technology

- Reduced tag manufacturing variability via Enduro™ Technology

- FastID<sup>™</sup> mode enables 2x to 3x faster EPC+TID inventory for authentication and other TID-based applications

- TagFocus<sup>™</sup> mode suppresses previously read tags to enable capture of more tags

- Scalable serialization built-in with Monza Self-Serialization

- Impinj's field-rewritable NVM, optimized for RFID, provides 100,000-cycle or 50-year retention reliability

- Enhanced privacy, loss prevention, brand protection

## **TABLE OF CONTENTS**

| 1 | Intro | duction                                                  |     |

|---|-------|----------------------------------------------------------|-----|

|   | 1.1   | Scope                                                    |     |

|   | 1.2   | Reference Documents                                      |     |

| 2 | Fund  | ctional Description                                      |     |

|   | 2.1   | Memory                                                   |     |

|   | 2.2   | Advanced Monza Features Support More Effective Inventory | .2  |

|   | 2.3   | Support for Optional Gen2 Commands                       |     |

|   | 2.4   | Data Integrity Features (Integra™ Technology)            | . 3 |

|   | 2.4.1 |                                                          |     |

|   | 2.4.2 | TID Parity                                               | . 3 |

|   | 2.4.3 | MarginRead Command                                       | . 3 |

|   | 2.4.4 | Recommended MarginRead Usage Guidelines                  | .5  |

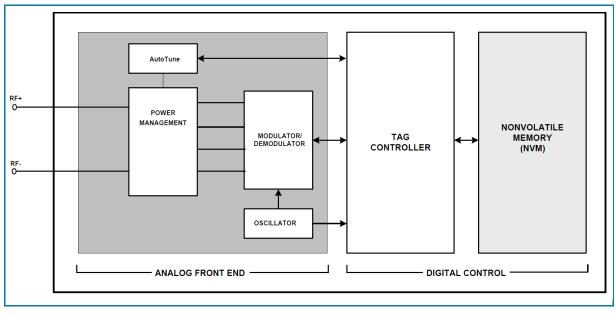

|   | 2.5   | Monza R6-P Tag Chip Block Diagram                        | .5  |

|   | 2.6   | Pad Descriptions                                         | .5  |

|   | 2.7   | Differential Antenna Input                               |     |

|   | 2.8   | Monza 6 Antenna Reference Designs                        | .6  |

|   | 2.9   | Monza R6-P Tag Chip Dimensions                           |     |

|   | 2.10  | Power Management                                         |     |

|   | 2.11  | AutoTune                                                 |     |

|   | 2.12  | Modulator/Demodulator                                    |     |

|   | 2.13  | Tag Controller                                           |     |

|   | 2.14  | Nonvolatile Memory                                       |     |

| 3 |       | face Characteristics                                     |     |

| - | 3.1   | Making Connections                                       |     |

|   | 3.2   | Impedance Parameters                                     |     |

|   | 3.3   | Reader-to-Tag (Forward Link) Signal Characteristics1     |     |

|   | 3.4   | Tag-to-Reader (Reverse Link) Signal Characteristics      |     |

| 4 | Tag   | Memory1                                                  |     |

|   | 4.1   | Monza R6-P Tag Chip Memory Map1                          |     |

|   | 4.2   | Logical vs. Physical Bit Identification1                 |     |

|   | 4.3   | Reserved Memory                                          |     |

|   | 4.3.1 |                                                          |     |

|   | 4.3.2 |                                                          |     |

|   | 4.3.3 |                                                          |     |

|   | 4.3.4 |                                                          |     |

|   | 4.3.5 |                                                          |     |

|   | 4.4   | EPC Memory (EPC Data, Protocol Control Bits, and CRC16)1 |     |

|   | 4.5   | Tag Identification (TID) Memory                          |     |

|   | 4.6   | User Memory1                                             |     |

| 5 |       | blute Maximum Ratings1                                   |     |

| Ĩ | 5.1   | Temperature                                              |     |

|   | 5.2   | Electrostatic Discharge (ESD) Tolerance                  |     |

|   | 5.3   | NVM Use Model                                            |     |

| 6 |       | Pring Information                                        |     |

| 7 |       | rnal References                                          |     |

| 8 |       | ces1                                                     |     |

## **1 INTRODUCTION**

### 1.1 Scope

This datasheet defines the physical and logical specifications for Gen2-compliant Monza R6-P tag silicon, a reader-talks-first, radio frequency identification (RFID) component operating in the UHF frequency range.

## **1.2 Reference Documents**

The following reference documents were used to compile this datasheet:

- EPC<sup>™</sup> Radio Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860 MHz 960 MHz (Gen2 Specification)

- The conventions used in the Gen2 Specification (normative references, terms and definitions, symbols, abbreviated terms, and notation) were adopted in the drafting of this Monza R6-P Tag Chip Datasheet. Users of this datasheet should familiarize themselves with the Gen2 Specification.

- Impinj Monza R6-P Wafer Specification

- Impinj Monza Wafer Map Orientation

- EPC<sup>™</sup> Tag Data Standards Specification 1.7

- EPCglobal "Interoperability Test System for EPC Compliant Class-1 Generation-2 UHF RFID Devices" v.1.2.4, August 4, 2006

- Monza R6-P tag chips are compliant with this Gen2 interoperability standard.

You may consult these documents for more information about compliance standards and specifications.

## **2 FUNCTIONAL DESCRIPTION**

The Monza R6-P tag chip fully supports all requirements of the Gen2 specification as well as many optional commands and features (see Support for Optional Gen2 Commands, section 2.3). In addition, Monza R6-P provides several enhancements:

- Superior sensitivity for high read and write reliability

- Industry-leading memory write speed, delivering the highest encoding rates

- Short-range mode option that reduces the IC's read range to less than 1/10 of its normal range

- Access and kill password controls to prevent unauthorized write access to the IC and allow deactivation of the IC, e.g. in retail after purchase

- TagFocus<sup>™</sup> inventory mode, a Gen2 compliant method for capturing more hard-to-read tags by suppressing those that have already been read, by extending their S1 flag B-state

- FastID<sup>™</sup> inventory mode, a Gen2 compliant, patent-pending method for EPC+TID based inventory that is 2-3 times faster than previous methods

- A patent-pending Enduro<sup>™</sup> technology makes inlay manufacture less sensitive to die-attach pressure, resulting in less variance and more predictable performance in final inlay product

- AutoTune<sup>™</sup> technology allows Monza R6-P inlays to maintain high performance independent of the tagged items dielectric. In addition, smaller form factor designs can meet bandwidth requirements with AutoTune. Smaller antennas reduce manufacturing cost and increase the number of applications.

- Integra<sup>™</sup> technology, a suite of diagnostics which ensures consistently accurate data delivery that business can depend on

## 2.1 Memory

Optimized for item-level tagging, the Monza R6-P tag chip offers EPC memory of up to 128 bits, serialized TID, and up to 64 bits of user memory. See Table 1 for the memory organization.

| MEMORY SECTION       | DEFAULT MEMORY PROFILE       | MAX USER MEMORY PROFILE      |  |  |  |  |  |  |

|----------------------|------------------------------|------------------------------|--|--|--|--|--|--|

| User                 | 32 bits                      | 64 bits                      |  |  |  |  |  |  |

|                      | Serial Number – 48 bits      | Serial Number—48 bits        |  |  |  |  |  |  |

| TID (not changeable) | Extended TID Header—16 bits  | Extended TID Header—16 bits  |  |  |  |  |  |  |

|                      | Company/Model Number—32 bits | Company/Model Number—32 bits |  |  |  |  |  |  |

| EPC                  | 128 bits                     | 96 bits                      |  |  |  |  |  |  |

|                      | Chip Configuration           | Chip Configuration           |  |  |  |  |  |  |

| Reserved             | Kill Password – 32 bits      | Kill Password – 32 bits      |  |  |  |  |  |  |

|                      | Access Password – 32 bits    | Access Password – 32 bits    |  |  |  |  |  |  |

#### Table 1: Monza R6-P Memory Organization

## 2.2 Advanced Monza Features Support More Effective Inventory

Monza tag chips support two unique, patent-pending features designed to boost inventory performance for traditional EPC and TID-based applications:

- TagFocus<sup>™</sup> mode minimizes redundant reads of strong tags, allowing the reader to focus on weak tags that are typically the last to be found. Using TagFocus, readers can suppress previously read tags by indefinitely refreshing their S1 B state.

- FastID<sup>™</sup> mode makes TID-based applications such as authentication practical by boosting TIDbased inventory speeds by 2 to 3 times. Readers can inventory both the EPC and the TID without having to perform an *Access* command. Setting the EPC word length to zero enables TID-only serialization.

## 2.3 Support for Optional Gen2 Commands

Monza R6-P tag chips support the optional commands listed in Table 2.

| COMMAND        | CODE     | LENGTH (BITS) | DETAILS                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Access         | 11000110 | 56            | <ul> <li>Supports full functionality of the <i>Access</i> command</li> <li>Allows control of user access to write and/or lock the tag</li> </ul>                                                                                                                                                                                                                                         |  |  |

| BlockWrite     | 11000111 | >57           | <ul> <li>Accepts valid one-word commands</li> <li>Accepts valid two-word commands if pointer is an even value</li> <li>Returns error code (000000002) if it receives a valid two-word comwith an odd value pointer</li> <li>Returns error code (000000002) if it receives a command for more two words</li> <li>Does not respond to block <i>Write</i> commands of zero words</li> </ul> |  |  |

| BlockPermalock | 11000111 | >66           | <ul> <li>User memory when configured to 64 bits</li> <li>Two blocks, each 32 bits</li> <li>Ignored when user memory configured to 32 bits</li> </ul>                                                                                                                                                                                                                                     |  |  |

| Lock           | 11000101 | 60            | <ul> <li>Monza R6-P supports the full functionality of the <i>Lock</i> Command</li> <li>Separately lockable EPC and User memory bank</li> <li>Separately lockable access and kill passwords</li> <li>The TID memory bank is perma-locked read only</li> </ul>                                                                                                                            |  |  |

#### Table 2: Supported Optional Gen2 Specification Commands

## 2.4 Data Integrity Features (Integra<sup>™</sup> Technology)

Monza R6-P has several data integrity features that enhance encoding and data reliability. These features include memory self-check, TID parity, and the *MarginRead* command.

#### 2.4.1 Memory Self-Check

Monza R6-P performs a memory check on its NVM at every power-up. If a bit is weakly encoded an internal flag is set. When the tag is singulated it will respond back with a zero length EPC. A reader could then consider this tag for exception handling.

#### 2.4.2 TID Parity

Monza R6-P is encoded with even parity over the 48-bit serial number portion of the TID. A reader should calculate even parity with bitwise exclusive-OR as follows.

- $X = TID bit(30_h) \oplus TID bit(31_h) \oplus ... \oplus TID bit(5E_h) \oplus TID bit(5F_h)$

- If X = 0 the TID data is good

- If X = 1 the TID data has an error in it

#### 2.4.3 MarginRead Command

Table 3, Table 4, and Table 5 provide details about the custom Impinj *MarginRead* command.

### Table 3: MarginRead Command Code

| CODE             | LENGTH   | DETAILS                                                                                                                                                      |

|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |          | • The MarginRead command allows checking for sufficient write margin of known data                                                                           |

| 1110000000000001 | ≥67 bits | • The tag must be in the OPEN/SECURED state to respond to the command                                                                                        |

|                  |          | <ul> <li>If a tag receives a MarginRead command with an invalid handle, it ignores<br/>that command</li> </ul>                                               |

|                  |          | • The tag responds with the Insufficient Power error code if the power is too low to execute a <i>MarginRead</i>                                             |

|                  |          | <ul> <li>The tag responds with the Other error code if the margin is bad for a bit in<br/>the mask or if a non-matching bit is sent by the reader</li> </ul> |

|                  |          | • The <i>MarginRead</i> command is only applicable for programmable sections of the memory                                                                   |

|                  |          |                                                                                                                                                              |

### Table 4: MarginRead Command Details

| MARGINREAD COMMAND | CODE                 | MEM BANK                                       | BIT POINTER                        | LENGTH         | MASK       | RN     | CRC-16 |

|--------------------|----------------------|------------------------------------------------|------------------------------------|----------------|------------|--------|--------|

| #bits              | 16                   | 2                                              | EBV                                | 8              | Variable   | 16     | 16     |

| Details            | 11100000<br>00000001 | 00: Reserved<br>01: EPC<br>10: TID<br>11: User | Starting Bit<br>Address<br>Pointer | Length in Bits | Mask Value | handle |        |

## Table 5: MarginRead Command Field Descriptions

| FIELD       | DESCRIPTION                                                                                                                          |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mem Bank    | The memory bank to access.                                                                                                           |  |  |  |

| Bit Pointer | An EBV that indicates the starting bit address of the mask                                                                           |  |  |  |

| Length      | Length of the mask field from 1-255.<br>A value of zero shall result in the command being ignored                                    |  |  |  |

| Mask        | This field must match the expected values of the bits<br>The chip checks that each bit matches what is in the mask field with margin |  |  |  |

| RN          | The tag will ignore any MarginRead command received with an invalid handle                                                           |  |  |  |

The tag response to the *MarginRead* Command uses the preamble specified by the TRext value in the *Query* command that initiated the round. See Table 6 for tag response details.

#### Table 6: Tag Response to a Passing MarginRead Command

| RESPONSE    | HEADER | RN     | CRC-16 |

|-------------|--------|--------|--------|

| #bits       | 1      | 16     | 16     |

| Description | 0      | handle |        |

### 2.4.4 Recommended MarginRead Usage Guidelines

There are several ways that the *MarginRead* command could be used with Monza R6-P. Monza R6-P comes pre-serialized and the *MarginRead* command allows a programming reader to check that the pre-serialized data is well written and does not need to be re-encoded. Another recommended use of *MarginRead* is secondary and independent verification of the encoding quality. *MarginRead* can also be used for diagnosis when doing failure analysis on tags.

## 2.5 Monza R6-P Tag Chip Block Diagram

## 2.6 Pad Descriptions

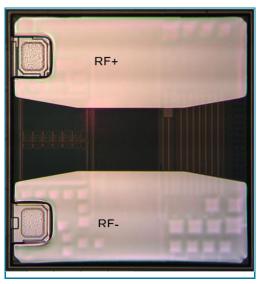

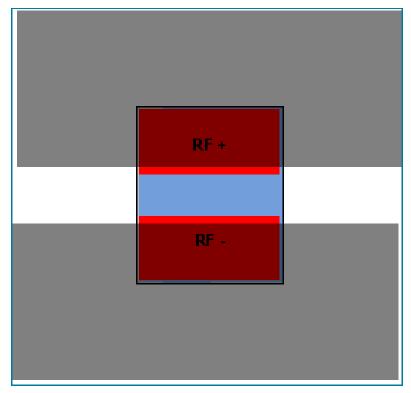

Monza R6-P tag chips have two external pads available to the user: one RF+ pad, and one RF- pads. RF+ and RF- form a single differential antenna port, as shown in Table 7 (see also Figure 1 and Figure 2). Note that none of these pads connects to the chip substrate.

#### Table 7: Pad Descriptions

| EXTERNAL SIGNALS | EXTERNAL PAD | DESCRIPTION                             |

|------------------|--------------|-----------------------------------------|

| RF+              | 1            | Differential DE Janut Dada far Antonna  |

| RF-              | 2            | Differential RF Input Pads for Antenna. |

## 2.7 Differential Antenna Input

All interaction with the Monza R6-P tag chip, including generation of its internal power, air interface, negotiation sequences, and command execution, occurs via its differential antenna port. The differential antenna port is connected with the RF+ pad connected to one terminal and the RF- pad connected to the other terminal.

Figure 2: Monza R6-P Tag Chip Die Orientation

## 2.8 Monza 6 Antenna Reference Designs

All Monza 6 family tag chips are designed to be drop-in compatible for antenna inlay designs. Impinj has a set of reference designs available for use by Monza customers under terms of the Impinj Antenna License Agreement.

These reference design documents are restricted. To access these documents, users must obtain access permission by creating an Impinj access account and submitting a request form through the Impinj Partner Access page<sup>1</sup>. Once Impinj has accepted their request, users can use their access credentials to view the Monza reference design documents page on the Support Portal<sup>2</sup>.

## 2.9 Monza R6-P Tag Chip Dimensions

Chip dimensions:

• 464.1 µm x 442 µm rectangular die size

- 166 µm x 422 µm pad size

- 112 µm pad spacing at center of die

- 154 µm pad spacing at edge of die

#### 2.10 Power Management

The tag is activated by proximity to an active reader. When the tag enters a reader's RF field, the Power Management block converts the induced electromagnetic field to the DC voltage that powers the chip.

#### 2.11 AutoTune

The AutoTune block adjusts Monza R6-P power harvesting from the inlay antenna by adjusting the chip's input capacitance. This adjustment occurs at power up and is held for the remainder of the time that Monza R6-P is powered.

### 2.12 Modulator/Demodulator

The Monza R6-P tag chip demodulates any of a reader's three possible modulation formats, DSB-ASK, SSB-ASK, or PR-ASK with PIE encoding. The tag communicates to a reader via backscatter of the incident RF waveform by switching the reflection coefficient of its antenna pair between reflective and absorptive states. Backscattered data is encoded as either FM0 or Miller subcarrier modulation (with the reader commanding both the encoding choice and the data rate).

### 2.13 Tag Controller

The Tag Controller block is a finite state machine (digital logic) that carries out command sequences and also performs a number of overhead duties.

### 2.14 Nonvolatile Memory

The Monza R6-P tag chip embedded memory is nonvolatile memory (NVM) cell technology, specifically optimized for exceptionally high performance in RFID applications. All programming overhead circuitry is integrated on chip. Monza R6-P tag chip NVM provides 100,000 cycle endurance or 50-year data retention.

The NVM block is organized into three segments:

- EPC Memory with up to 128 bits

- User Memory with up to 64 bits

- Reserved Memory

The ROM-based Tag Identification (TID) memory contains the EPCglobal class ID, the manufacturer identification, and the model number. It also contains an extended TID consisting of a 16-bit header and 48-bit serialization.

## **3 INTERFACE CHARACTERISTICS**

This section describes the RF interface of the tag chip and the modulation characteristics of both communication links: reader-to-tag (Forward Link) and tag-to-reader (Reverse Link).

### 3.1 Making Connections

Figure 3 shows antenna connection for Monza R6-P tag chips.

This connection configuration for inlay production contacts the Monza R6-P tag chip RF+ pad to one antenna terminal and the RF- pad to the opposite polarity terminal. Enduro<sup>™</sup> pads allow relatively coarse antenna geometry, and thus enable relaxed resolution requirements for antenna patterning compared to bumped products. The diagram in Figure 3 shows the recommended antenna trace arrangement and chip placement – having antenna traces partially overlapping the Enduro pads but not extending into the clear space between Enduro pads.

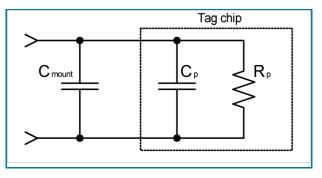

### 3.2 Impedance Parameters

To realize the full performance potential of the Monza R6-P tag chip, it is imperative that the antenna present the appropriate impedance at its terminals. A simplified lumped element tag chip model, shown in Figure 4, is the conjugate of the optimum source impedance, which is *not* equal to the chip input impedance. This indirect, source-pull method of deriving the port model is necessary due to the non-linear, time-varying nature of the tag RF circuits. The model is a good mathematical fit for the chip over a broad frequency range.

The lumped element values are listed in Table 8, where  $C_{mount}$  is the parasitic capacitance due to the antenna trace overlap with the chip surface,  $C_p$  appears at the chip terminals and is intrinsic to the chip, and  $R_p$  represents the energy conversion and energy absorption of the RF circuits. The lumped element values for Monza R6-P without Enduro pads are listed in Table 9, where  $C_p$  appears at the chip terminals and is intrinsic to the chip, and  $R_p$  represents the energy conversion and energy conversion and energy absorption of the RF circuits.

#### Figure 4: Tag Chip Linearized RF Model

Table 8 shows the values for the chip port model for the Monza R6-P tag chip, which apply to all frequencies of the primary regions of operation (North America, Europe, and Japan).

| PARAMETER              | TYPICAL VALUE | COMMENTS                                                                                                                                              |

|------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>p</sub>         | 1.23 pF       | Intrinsic chip capacitance when AutoTune is mid-range, including Enduro pads.                                                                         |

| R <sub>p</sub>         | 1.2 kOhm      | Calculated for linearized RF model shown in Figure 4. Measured $R_p$ = 1.56 kOhm using network analyzer.                                              |

| C <sub>mount</sub>     | 0.21 pF       | Typical capacitance due to adhesive and antenna mount parasitics. Total load capacitance presented to antenna model of Figure 4 is: $C_p + C_{mount}$ |

| Chip Read Sensitivity  | - 20 dBm      | Measured at 25 °C; R=>T link using DSB-ASK modulation with 90% modulation                                                                             |

| Chip Write Sensitivity | - 15.2 dBm    | depth, Tari=25 $\mu\text{s},$ and a T=>R link operating at 170 kbps with Miller M=8 encoding.                                                         |

#### Table 8: Monza R6-P Enduro Chip Port Parameters

Table 9 shows the values for the chip port model for the Monza R6-P tag chip without Enduro bonding pads, which apply to all frequencies of the primary regions of operation (North America, Europe, and Japan).

| Fable 9: Monza R6-P Non-Enduro Chip Port Parameters |               |                                                                                                                                                                   |  |  |  |  |  |

|-----------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PARAMETER                                           | TYPICAL VALUE | COMMENTS                                                                                                                                                          |  |  |  |  |  |

| C <sub>p</sub>                                      | 1.13 pF       | Intrinsic chip capacitance when AutoTune is mid-range, including Enduro pads.                                                                                     |  |  |  |  |  |

| R <sub>p</sub>                                      | 1.2 kOhm      | Calculated for linearized RF model shown in Figure 4. Measured $R_p$ = 1.56 kOhm using network analyzer.                                                          |  |  |  |  |  |

| Chip Read Sensitivity                               | - 20 dBm      | Measured at 25 °C; R=>T link using DSB-ASK modulation with 90% modulation depth, Tari=25 $\mu s,$ and a T=>R link operating at 170 kbps with Miller M=8 encoding. |  |  |  |  |  |

#### Т

## 3.3 Reader-to-Tag (Forward Link) Signal Characteristics

| PARAMETER                          | MINIMUM              | TYPICAL                           | MAXIMUM   | UNITS | COMMENTS                                                                                    |  |  |  |

|------------------------------------|----------------------|-----------------------------------|-----------|-------|---------------------------------------------------------------------------------------------|--|--|--|

| RF Characteristics                 |                      |                                   |           |       |                                                                                             |  |  |  |

| Carrier Frequency                  | 860                  |                                   | 960       | MHz   | North America: 902–928 MHz<br>Europe: 865–868 MHz                                           |  |  |  |

| Maximum RF Field<br>Strength       |                      |                                   | +20       | dBm   | Received by a tag with dipole antenna while sitting<br>on a maximum power reader antenna    |  |  |  |

| Modulation                         |                      | DSB-ASK,<br>SSB-ASK,<br>or PR-ASK |           |       | Double and single sideband amplitude shift keying;<br>phase-reversal amplitude shift keying |  |  |  |

| Data Encoding                      |                      | PIE                               |           |       | Pulse-interval encoding                                                                     |  |  |  |

| Modulation Depth                   | 80                   |                                   | 100       | %     | (A-B)/A, A=envelope max., B=envelope min.                                                   |  |  |  |

| Ripple, Peak-to-Peak               |                      |                                   | 5         | %     | Portion of A-B                                                                              |  |  |  |

| Rise Time (t <sub>r,10-90%)</sub>  | 0                    |                                   | 0.33Tari  | sec   |                                                                                             |  |  |  |

| Fall Time (t <sub>f,10-90%</sub> ) | 0                    |                                   | 0.33Tari  | sec   |                                                                                             |  |  |  |

| Tari*                              | 6.25                 |                                   | 25        | μs    | Data 0 symbol period                                                                        |  |  |  |

| PIE Symbol Ratio                   | 1.5:1                |                                   | 2:1       |       | Data 1 symbol duration relative to Data 0                                                   |  |  |  |

| Duty Cycle                         | 48                   |                                   | 82.3      | %     | Ratio of data symbol high time to total symbol time                                         |  |  |  |

| Pulse Width                        | MAX(0.26<br>5Tari,2) |                                   | 0.525Tari | μs    | Pulse width defined as the low modulation time (50% amplitude)                              |  |  |  |

### Table 10: Forward Link Signal Parameters

\*Values are nominal minimum and nominal maximum, and do not include frequency tolerance. Apply appropriate frequency tolerance to derive absolute periods and frequencies.

## 3.4 Tag-to-Reader (Reverse Link) Signal Characteristics

| PARAMETER                                            | MINIMUM | TYPICAL                              | ΜΑΧΙΜυΜ      | UNITS | COMMENTS                                                                                      |  |  |  |

|------------------------------------------------------|---------|--------------------------------------|--------------|-------|-----------------------------------------------------------------------------------------------|--|--|--|

|                                                      |         | Modulation Char                      | racteristics |       |                                                                                               |  |  |  |

| Modulation                                           |         | ASK                                  |              |       | FET Modulator                                                                                 |  |  |  |

| Data Encoding                                        |         | Baseband FM0 or<br>Miller Subcarrier |              |       |                                                                                               |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         | 0.8                                  |              |       | $ \Delta\Gamma  =  \Gamma_{reflect} - \Gamma_{absorb} $ (per read/write sensitivity, Table 8) |  |  |  |

| Duty Cycle                                           | 45      | 50                                   | 55           | %     |                                                                                               |  |  |  |

| Symbol Davied <sup>1</sup>                           | 1.5625  |                                      | 25           | μs    | Baseband FM0                                                                                  |  |  |  |

| Symbol Period <sup>1</sup>                           | 3.125   |                                      | 200          | μs    | Miller-modulated subcarrier                                                                   |  |  |  |

| Miller Subcarrier Frequency*                         | 40      |                                      | 640          | kHz   |                                                                                               |  |  |  |

#### Table 11: Reverse Link Signal Parameters

\* Values are nominal minimum and nominal maximum, and do not include frequency tolerance. Apply appropriate frequency tolerance to derive absolute periods and frequencies.

## 4 TAG MEMORY

## 4.1 Monza R6-P Tag Chip Memory Map

| MEMORY BANK            | MEMORY            | MEMORY BANK                        |                     | BIT ADDRESS       |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|------------------------|-------------------|------------------------------------|---------------------|-------------------|--------|----|--------|-------|-------|------------------|----------------|--------|-------|------|-------|--------|-----|-------|---|

| NUMBER                 | BANK NAME         | BIT ADDRESS                        | 15                  | 14                | 13     | 12 | 11     | 10    | )     | 9                | 8              | 7      | 6     | 5    | 4     | 3      | 2   | 1     | 0 |

| 44                     |                   | 10 <sub>h</sub> -1F <sub>h</sub>   |                     | •                 |        |    |        | •     | ι     | Jser             | [15:           | 0]     |       |      |       | •      | •   |       |   |

| 11 <sub>2</sub>        | User (NVM)        | 00 <sub>h</sub> -0F <sub>h</sub>   |                     |                   |        |    |        |       | U     | Jser[            | [31:1          | 6]     |       |      |       |        |     |       |   |

|                        |                   | 50 <sub>h</sub> -5F <sub>h</sub>   |                     |                   |        |    |        |       | TID   | _Se              | rial[          | 15:0]  |       |      |       |        |     |       |   |

|                        |                   | $40_{h}$ - $4F_{h}$                |                     |                   |        |    |        | ٦     | TID_  | _Sei             | rial[3         | 1:16]  |       |      |       |        |     |       |   |

| 10                     |                   | 30 <sub>h</sub> -3F <sub>h</sub>   |                     | TID_Serial[47:32] |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

| <b>10</b> <sub>2</sub> | TID (ROM)         | $20_{h}-2F_{h}$                    | Extended TID Header |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|                        |                   | 10 <sub>h</sub> -1F <sub>h</sub>   | N                   | lanufa            | cturer | ID |        |       |       |                  |                | Мо     | del N | umbe | r     |        |     |       |   |

|                        |                   | 00 <sub>h</sub> -0F <sub>h</sub>   | 1                   | 1                 | 1      | 0  | 0      | 0     |       | 1                | 0              |        |       | Ma   | nufac | cturer | ID  |       |   |

|                        |                   | 90 <sub>h</sub> -9F <sub>h</sub>   | EPC[15:0]           |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|                        | EPC (NVM)         | 80 <sub>h</sub> -8F <sub>h</sub>   | EPC[31:16]          |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|                        |                   | $70_{h}$ - $7F_{h}$                |                     | EPC[47:32]        |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|                        |                   | 60 <sub>h</sub> -6F <sub>h</sub>   | EPC[63:48]          |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

| <b>01</b> <sub>2</sub> |                   | $50_{h}$ - $5F_{h}$                | EPC[79:64]          |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

| 012                    |                   | $40_{h}$ - $4F_{h}$                | EPC[95:80]          |                   |        |    |        |       |       |                  |                |        |       |      |       |        |     |       |   |

|                        |                   | 30 <sub>h</sub> -3F <sub>h</sub>   |                     |                   |        |    |        |       | E     | PC[ <sup>′</sup> | 111:           | 96]    |       |      |       |        |     |       |   |

|                        |                   | $20_{h}-2F_{h}$                    |                     |                   |        |    |        |       | EF    | PC[1             | 27:1           | 12]    |       |      |       |        |     |       |   |

|                        |                   | 10 <sub>h</sub> -1F <sub>h</sub>   |                     |                   |        |    |        | Proto | ocol  | -Coi             | ntrol          | Bits   | (PC)  |      |       |        |     |       |   |

|                        |                   | 00 <sub>h</sub> -0F <sub>h</sub>   |                     |                   |        |    |        |       |       | CR               | C-16           | 6      |       |      |       |        |     |       |   |

|                        |                   | 140 <sub>h</sub> -14F <sub>h</sub> |                     |                   |        |    | R      | FU[12 | 2:0]  | =00              | 0 <sub>h</sub> |        |       |      |       |        | ΑTV | [2:0] | ] |

|                        |                   | 60 <sub>h</sub> -6F <sub>h</sub>   |                     |                   |        |    |        | Facto | ory ( | Calib            | oratio         | on B[  | 15:0] |      |       |        |     |       |   |

|                        |                   | 50 <sub>h</sub> -5F <sub>h</sub>   |                     |                   |        |    |        | Facto | ory ( | Calik            | oratio         | on A[  | 15:0] |      |       |        |     |       |   |

| 002                    | RESERVED<br>(NVM) | 40 <sub>h</sub> -4F <sub>h</sub>   |                     |                   |        | In | iterna | l Con | figu  | ratic            | on[15          | 5:3]   |       |      |       |        | Μ   | S     | А |

|                        |                   | 30 <sub>h</sub> -3F <sub>h</sub>   |                     |                   |        |    |        | Acc   | ess   | Pas              | sswo           | ord[15 | 5:0]  |      |       |        |     |       |   |

|                        |                   | $20_{h}-2F_{h}$                    |                     |                   |        |    |        | Acce  | ess   | Pas              | SWO            | rd[31  | :16]  |      |       |        |     |       |   |

|                        |                   | 10 <sub>h</sub> -1F <sub>h</sub>   |                     |                   |        |    |        | K     | ill P | ass              | word           | l[15:0 | )]    |      |       |        |     |       |   |

|                        |                   | 00 <sub>h</sub> -0F <sub>h</sub>   |                     |                   |        |    |        | Ki    | ll Pa | assv             | vord           | [31:10 | 6]    |      |       |        |     |       |   |

### Table 12: Physical/Logical Memory Map – Default Memory Profile

| MEMORY          | MEMORY     | MEMORY                           |                   |                     |            |    |         |        | BIT    | ADD              | RESS    |        |     |      |       |        |   |     |       |    |

|-----------------|------------|----------------------------------|-------------------|---------------------|------------|----|---------|--------|--------|------------------|---------|--------|-----|------|-------|--------|---|-----|-------|----|

| BANK NUMBER     |            | BANK BIT<br>ADDRESS              | 15                | 14                  | 13         | 12 | 11      | 10     | 9      | 8                | 7       | 6      | 4   | 5    | 4     | 3      | 2 | 2   | 1     | 0  |

|                 |            | 30 <sub>h</sub> -3F <sub>h</sub> |                   |                     |            |    | •       |        | U      | ser[1            | 5:0]    |        | •   | •    |       |        |   | •   |       |    |

| 44              |            | $20_h - 2F_h$                    |                   |                     |            |    |         |        | Us     | er[31            | :16]    |        |     |      |       |        |   |     |       |    |

| 11 <sub>2</sub> | User (NVM) | $10_h - 1F_h$                    |                   |                     |            |    |         |        | Us     | er[47            | :32]    |        |     |      |       |        |   |     |       |    |

|                 |            | $00_{h}-0F_{h}$                  |                   | User[63:48]         |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

|                 |            | $50_{h}$ - $5F_{h}$              | TID_Serial[15:0]  |                     |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

|                 |            | $40_{h}$ - $4F_{h}$              | TID_Serial[31:16] |                     |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

| 102             |            | $30_h - 3F_h$                    |                   | TID_Serial[47:32]   |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

| 102             | TID (ROM)  | $20_{h}-2F_{h}$                  |                   | Extended TID Header |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

|                 |            | $10_{h}$ - $1F_{h}$              | N                 | lanufa              | cturer     | ID |         |        |        |                  | Mo      | del N  | umb | er   |       |        |   |     |       |    |

|                 |            | $00_{h}-0F_{h}$                  | 1                 | 1                   | 1          | 0  | 0       | 0      | 1      | 0                |         |        | Ma  | anul | factu | irer I | D |     |       |    |

|                 |            | $70_{h}$ - $7F_{h}$              |                   |                     |            |    |         |        | El     | PC[1             | 5:0]    |        |     |      |       |        |   |     |       |    |

|                 |            | 60 <sub>h</sub> -6F <sub>h</sub> |                   |                     | EPC[31:16] |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

|                 |            | 50 <sub>h</sub> -5F <sub>h</sub> | EPC[47:32]        |                     |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

| 012             | EPC (NVM)  | $40_{h}$ - $4F_{h}$              |                   | EPC[63:48]          |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

| 012             |            | $30_h - 3F_h$                    |                   | EPC[79:64]          |            |    |         |        |        |                  |         |        |     |      |       |        |   |     |       |    |

|                 |            | $20_{h}$ - $2F_{h}$              |                   |                     |            |    |         |        | EP     | PC[95            | :80]    |        |     |      |       |        |   |     |       |    |

|                 |            | $10_{h}$ - $1F_{h}$              |                   |                     |            |    |         | Proto  | ocol-( | Contr            | ol Bits | (PC)   |     |      |       |        |   |     |       |    |

|                 |            | $00_{h}-0F_{h}$                  |                   |                     |            |    |         |        | (      | CRC-             | 16      |        |     |      |       |        |   |     |       |    |

|                 |            | $140_{h}$ - $14F_{h}$            |                   |                     |            |    | F       | RFU[1  | 2:0]=  | 000 <sub>H</sub> |         |        |     |      |       |        |   | AT∖ | /[2:0 | D] |

|                 | -          | $60_{h}$ - $6F_{h}$              |                   |                     |            |    |         | Facto  | ory Ca | alibra           | tion B  | [15:0] |     |      |       |        |   |     |       |    |

|                 |            | $50_{h}$ - $5F_{h}$              |                   |                     |            |    |         | Facto  | ory Ca | alibra           | tion A  | [15:0] |     |      |       |        |   |     |       |    |

| 002             | RESERVED   | $40_{h}$ - $4F_{h}$              |                   |                     |            |    | Interna | al Con | figura | ation[           | 15:3]   |        |     |      |       |        | N | Л   | S     | А  |

| 002             | (NVM)      | 30 <sub>h</sub> -3F <sub>h</sub> |                   |                     |            |    |         | Acc    | ess l  | Pass             | vord[1  | 5:0]   |     |      |       |        | _ |     |       | L  |

|                 |            | $20_{h}$ - $2F_{h}$              |                   |                     |            |    |         | Acce   | ess P  | assw             | ord[3   | 1:16]  |     |      |       |        |   |     |       |    |

|                 |            | 10 <sub>h</sub> -1F <sub>h</sub> |                   |                     |            |    |         | K      | ill Pa | SSWO             | rd[15:  | 0]     |     |      |       |        |   |     |       |    |

|                 |            | $00_{h}-0F_{h}$                  |                   |                     |            |    |         | Ki     | ll Pas | swoi             | d[31:   | 16]    |     |      |       |        |   |     |       |    |

#### Table 13: Physical/Logical Memory Map – Max\_User Memory Profile

## 4.2 Logical vs. Physical Bit Identification

For the purposes of distinguishing most significant from least significant bits, a logical representation is used in this datasheet where MSBs correspond to large bit numbers and LSBs to small bit numbers. For example, Bit 15 is the logical MSB of a memory row in the memory map. Bit 0 is the LSB. A multi-bit word represented by WORD[N:0] is interpreted as MSB first when read from left to right. This convention should

not be confused with the physical bit address indicated by the rows and column addresses in the memory map; the physical bit address describes the addressing used to access the memory.

### 4.3 Reserved Memory

Reserved Memory contains the access and kill passwords, which are programmed to zero by default. It also contains three user configuration bits, which may only be changed in the **secured** state. If a tag has a non-zero access password, a reader must issue an *Access* command sequence with the correct access password to put the tag in the **secured** state prior to writing these bits.

- M = the memory map selection bit. This bit is set to one at the factory and may be written once to change the memory map.

- S = the short-range bit. This bit is set to zero at the factory. When set this bit puts the chip into a short-range mode. The chip will not respond at all unless it is in short range.

- A = the AutoTune disable bit. When the AutoTune disable bit is zero AutoTune works as normal. When the bit is one, AutoTune is disabled and the capacitance on the front end assumes the midrange value.

To write any one of these three bits a *Write* command or single word *BlockWrite* command must be issued to word 4 of reserved memory. The bits of the payload that correspond to the Internal Configuration will be ignored by the tag. The AutoTune value is marked ATV[2:0] in word 14<sub>h</sub>. The AutoTune value represents the tuning capacitance scale, from zero to four.

#### 4.3.1 Access Password

The access password is a 32-bit value stored in Reserved Memory  $20_h$  to  $3F_h$  MSB first. The default value is all zeroes. Tags with a non-zero access password will require a reader to issue this password before transitioning to the secured state.

#### 4.3.2 Kill Password

The kill password is a 32-bit value stored in Reserve Memory 00<sub>h</sub> to 1F<sub>h</sub>, MSB first. The default value is all zeroes. A reader shall use a tag's kill password once to kill the tag and render it silent thereafter. A tag will not execute a kill operation if its kill password is all zeroes.

#### 4.3.3 Memory Map Selection

Monza R6-P comes from the factory with space for a 128-bit EPC in the EPC bank and 32 bits of memory in the User bank. This memory corresponds to the memory map selection bit, M, being equal to one. The user may write this bit once. If the value is set to zero then the EPC bank will only support a 96-bit EPC, but the User bank will increase to 64 bits of memory. After a memory map is selected the memory map is locked and no further changes are permitted. In addition, if any valid Lock command is issued to the tag, the memory map will be locked.

#### 4.3.4 Short Range

Monza R6-P comes with a short-range capability to enhance consumer privacy. The short-range bit in reserved memory may be written when the tag is in the secured state. The factory programmed value of the short-range bit is zero, which means the tag operates at full range. When a reader writes the S bit to a one the tag will only respond when it is near the reader, reducing the IC's read range to less than 1/10 of its normal range. Short range may be turned off again by writing the S bit to a zero.

#### 4.3.5 AutoTune Disable and AutoTune Value

The AutoTune disable bit is in word 04<sub>h</sub>, marked A in the memory map, and the AutoTune value, marked ATV[2:0] in word 14<sub>h</sub>. The factory programmed value of the AutoTune disable bit is zero. The AutoTune value represents the tuning capacitance scale, from zero to four. A value of zero removes 80 fF of capacitance across the RF input of the tag and a value of four adds 100 fF across the RF input of the chip. See Table 14 for the mapping between AutoTune value and the change in input capacitance. A reader acquires the AutoTune value by issuing a single word *Read* command to word 14<sub>h</sub> in the reserved memory bank. The AutoTune value is not writable.

To disable AutoTune a reader issues a *Write* command or a single word *BlockWrite* command to word 04<sub>h</sub>. Only the bits for AutoTune disable, memory map selection and short range may change and the rest of bits in the payload will be ignored. These bits may only be written in the **secured** state; if a tag has a non-zero access password, a reader must issue an *Access* command sequence with the correct access password to put the tag in the **secured** state prior to writing this word.

When the AutoTune disable bit is zero AutoTune works as normal and when the bit is one AutoTune is overridden and the capacitance across the RF input is set to 0 fF. When AutoTune is disabled, the readout of AutoTune value does not represent the value of capacitance across the RF input to the tag.

| AUTOTUNE VALUE | CHANGE IN INPUT CAPACITANCE (FF) |

|----------------|----------------------------------|

| 0h             | -80                              |

| 1h             | -40                              |

| 2h             | 0                                |

| 3h             | +60                              |

| 4h             | +100                             |

#### Table 14: AutoTune Value

## 4.4 EPC Memory (EPC Data, Protocol Control Bits, and CRC16)

As per the Gen2 specification, EPC memory contains a 16-bit cyclic-redundancy check word (CRC16) at memory addresses  $00_h$  to  $0F_h$ , the 16 protocol-control bits (PC) at memory addresses  $10_h$  to  $1F_h$ , and an EPC value beginning at address  $20_h$ .

The protocol control fields include a five-bit EPC length, a one-bit user-memory indicator (UMI=1), a onebit extended protocol control indicator, and nine bits of programmable memory from  $17_h$  to  $1F_h$  for the numbering system identifier (NSI) toggle bit, T, and Reserved for Future Use or Application Family Identifier (RFU or AFI), bits  $18_h$  to  $1F_h$ . The factory default value is  $3400_h$ .

The tag calculates the CRC16 upon power-up over the stored PC bits and the EPC specified by the EPC length field in the stored PC. For more details about the PC field or the CRC16, see the Gen2 specification.

A reader accesses EPC memory by setting MemBank =  $01_2$  in the appropriate command, and providing a memory address using the extensible-bit-vector (EBV) format. The CRC-16, PC, and EPC are stored MSB first (i.e., the EPC's MSB is stored in location  $20_h$ ).

The EPC memory bank of Monza R6-P supports a maximum EPC size of 128 bits in the Default Memory Profile and a maximum EPC size of 96 bits in the Max User Memory Profile (see Table 1). The default configuration from the factory, however, is for a 96-bit EPC. It is possible to adjust the EPC size up or down from 96 bits, according to the parameters laid out in the Gen2 standard. The EPC value written into the chip during factory test is listed below in Table 15. The "X" nibbles in the pre-programmed EPC are pre-serialized values that follow the Impinj Monza Self-Serialization formula for Monza R6-P.

For more details on the pre-serialization formula used to generate the factory-programmed EPC, refer to the Monza TID Memory Maps for Self-Serialization<sup>3</sup>.

| Table 15: | : EPC at | Factory-Program |

|-----------|----------|-----------------|

|-----------|----------|-----------------|

| IMPINJ PART NUMBER | EPC VALUE PRE-PROGRAMMED AT THE FACTORY (HEX) |

|--------------------|-----------------------------------------------|

| IPJ-W1710-K00      | E280 1170 XXXX XXXX XXXX XXXX                 |

## 4.5 Tag Identification (TID) Memory

The ROM-based Tag Identification memory contains Impinj-specific data. The Impinj MDID (Manufacturer Identifier) for Monza R6-P is 10000000001 (the location of the manufacturer ID is shown in the Monza R6-P Tag Chip Memory Map, section 4.1, and the bit details are given in Table 16). Note that a logic 1 in the most significant bit of the manufacturer ID (as in the example bordered in solid black in the table) indicates the presence of an extended TID consisting of a 16-bit header and a 48-bit serialization. The 48-bit serialization has even parity as discussed in TID Parity, section 2.4.2. The Monza R6-P tag chip model number is located in the area bordered by the dashed line in TID memory row 10h-1Fh as shown in Table 16. The non-shaded bit locations in TID row 00h-0Fh store the EPCglobal<sup>™</sup> Class ID (0xE2).

#### Table 16: TID Memory Details

| MEMORY BANK     |           |                                  | BIT ADDRESS       |                         |    |    |    |      |      |        |       |   |   |   |   |   |   |   |

|-----------------|-----------|----------------------------------|-------------------|-------------------------|----|----|----|------|------|--------|-------|---|---|---|---|---|---|---|

| NUMBER          | BANK NAME | BIT ADDRESS                      | 15                | 14                      | 13 | 12 | 11 | 10   | 9    | 8      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                 |           | $50_{h}$ - $5F_{h}$              | TID_SERIAL[15:0]  |                         |    |    |    |      |      |        |       |   |   |   |   |   |   |   |

|                 |           | $40_{h}$ - $4F_{h}$              | TID_SERIAL[31:16] |                         |    |    |    |      |      |        |       |   |   |   |   |   |   |   |

|                 |           | 30 <sub>h</sub> -3F <sub>h</sub> |                   |                         |    |    |    | TID_ | _SER | RIAL[4 | 17:32 | ] |   |   |   |   |   |   |

| 10 <sub>2</sub> | TID (ROM) | 20 <sub>h</sub> -2F <sub>h</sub> | 0                 | 0                       | 1  | 0  | 0  | 0    | 0    | 0      | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|                 |           |                                  |                   | Monza R6-P Model Number |    |    |    |      |      |        |       |   |   |   |   |   |   |   |

|                 |           | 10 <sub>h</sub> -1F <sub>h</sub> | 0                 | 0                       | 0  | 1  | 0  | 0    | 0    | 1      | 0     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|                 |           | 00 <sub>h</sub> -0F <sub>h</sub> | 1                 | 1                       | 1  | 0  | 0  | 0    | 1    | 0      | 1     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### 4.6 User Memory

At the factory the User bank contains two 16-bit words at word address  $0_h$  to  $1_h$ . The User bank has individually controllable lock bits. When the memory map selection bit is set to zero the User bank is increased to four 16-bit words at word addresses  $0_h$  to  $3_h$ . When configured to this larger memory map the *BlockPermalock* command is accepted and there are two 32-bit blocks. Block zero is at word address  $0_h$  to  $1_h$  and block one is at word address  $2_h$  to  $3_h$ .

When the memory map is configured to Max User Memory Profile, the end user can use the combination of the *BlockPermalock* command and *Lock* command to create two blocks of memory, one of which is permanently locked and the other permanently unlocked. The *BlockPermalock* command must be issued first to lock one of the two blocks of user memory, then the *Lock* command must be issued to PermaUnlock the rest of the user memory. This is illustrated in Table 17 for reference. Note: other sequences of

*BlockPermalock* and *Lock* commands may be used; so long as one block is blockpermalocked first, the other block may be locked independently.

| MEMORY BANK BIT ADDRESS | MEMORY BLOCK | MEMORY COMMAND                                     |  |  |  |  |  |

|-------------------------|--------------|----------------------------------------------------|--|--|--|--|--|

| 30h-3Fh                 | Disali 1     | Dissi/Derrosiasi, en Dissi, 4                      |  |  |  |  |  |

| 20h-2Fh                 | Block 1      | BlockPermalock on Block 1                          |  |  |  |  |  |

| 10h-1Fh                 | Plack 0      | PermaUnlock via <i>Lock</i> command on User memory |  |  |  |  |  |

| 00h-0Fh                 | Block 0      |                                                    |  |  |  |  |  |

#### Table 17: User Memory Blocks, Max User Memory Profile Locking Example

## **5 ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed in this section may cause permanent damage to the tag. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this datasheet is not guaranteed or implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 5.1 Temperature

Several different temperature ranges will apply over unique operating and survival conditions. Table 18 lists the ranges that will be referred to in this specification. Tag functional and performance requirements are met over the operating range, unless otherwise specified.

#### **Table 18: Temperature Parameters**

| PARAMETER                      | MINIMUM | TYPICAL | MAXIMUM | UNITS    | COMMENTS                                                      |  |  |  |  |

|--------------------------------|---------|---------|---------|----------|---------------------------------------------------------------|--|--|--|--|

| Extended Operating Temperature | -40     |         | +85     | °C       | Default range for all functional and performance requirements |  |  |  |  |

| Storage Temperature            | -40     |         | +85/125 | °C       | At 125°C data retention is 1 year                             |  |  |  |  |

| Assembly Survival Temperature  |         |         | +260    | °C       | Applied for one minute                                        |  |  |  |  |

| Temperature Rate of Change     |         |         | 4       | °C / sec | During operation                                              |  |  |  |  |

## 5.2 Electrostatic Discharge (ESD) Tolerance

The tag is guaranteed to survive ESD as specified in Table 19.

Table 19: ESD Limits

| PARAMETER | MINIMUM | TYPICAL | MAXIMUM | UNITS | COMMENTS               |

|-----------|---------|---------|---------|-------|------------------------|

| ESD       |         |         | 2,000   | V     | HBM (Human Body Model) |

## 5.3 NVM Use Model

Tag memory is designed to endure 100,000 write cycles or retain data for 50 years.

## **6 ORDERING INFORMATION**

Contact <u>sales@impinj.com</u> for ordering support.

#### **Table 20: Ordering Information**

| Р                              | ART NUMBER   | FORM  | PRODUCT                                 | PROCESSING FLOW                                 |

|--------------------------------|--------------|-------|-----------------------------------------|-------------------------------------------------|

| IF                             | PJ-W1710-K00 | Wafer | Monza R6-P tag chip                     | Padded, thinned (to ~109 $\mu m)$ and diced     |

| IPJ-W1710-A00 Wafer Monza R6-P |              | Wafer | Monza R6-P tag chip (non-Enduro, diced) | Non-Enduro, thinned (to ~100 $\mu m)$ and diced |

## 7 EXTERNAL REFERENCES

<sup>1</sup> Support Link: Impinj Restricted Access Request Form (<u>https://access.impinj.com/prtlaccessrequest</u>)

<sup>2</sup> Support Link: *Monza Reference Design Documents & Downloads* (<u>https://support.impinj.com/hc/en-us/sections/200454558-Monza-Reference-Design-Documents-Downloads</u>) – Note: These documents are restricted and require access permission from Impinj.

<sup>3</sup> Support Link: *TID Memory Maps for Monza Self-Serialization* (<u>https://support.impinj.com/hc/en-us/articles/203444983-TID-Memory-Maps-for-Monza-Self-Serialization</u>)

## 8 NOTICES

Copyright © 2020, Impinj, Inc. All rights reserved.

Impinj gives no representation or warranty, express or implied, for accuracy or reliability of information in this document. Impinj reserves the right to change its products and services and this information at any time without notice.

EXCEPT AS PROVIDED IN IMPINJ'S TERMS AND CONDITIONS OF SALE (OR AS OTHERWISE AGREED IN A VALID WRITTEN INDIVIDUAL AGREEMENTWITH IMPINJ), IMPINJ ASSUMES NO LIABILITY WHATSOEVER AND IMPINJ DISCLAIMS ANY EXPRESS OR IMPLIEDWARRANTY, RELATED TO SALE AND/OR USE OF IMPINJ PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT.

NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY PATENT, COPYRIGHT, MASKWORK RIGHT, OR OTHER INTELLECTUALPROPERTY RIGHT IS GRANTED BY THIS DOCUMENT.

Impinj assumes no liability for applications assistance or customer product design. Customers should provide adequate design and operating safeguards to minimize risks.

Impinj products are not designed, warranted or authorized for use in any product or application where a malfunction may reasonably be expected to cause personal injury or death, or property or environmental damage ("hazardous uses"), including but not limited to military applications; life-support systems; aircraft control, navigation or communication; air-traffic management; or in the design, construction, operation, or maintenance of a nuclear facility. Customers must indemnify Impinj against any damages arising out of the use of Impinj products in any hazardous uses

Impinj, and Impinj products and features are trademarks or registered trademarks of Impinj, Inc. For a complete list of Impinj Trademarks, visit <u>www.impinj.com/trademarks</u>. All other product or service names may be trademarks of their respective companies.

The products referenced in this document may be covered by one or more U.S. patents. See <u>www.impinj.com/patents</u> for details.